基本情報技術者講座

★ 猫本 1-04 CPUの動作原理(その1) ★

基本情報技術者 平成30年度春期 問9

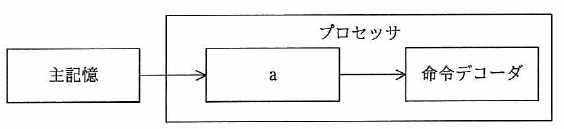

図はプロセッサによってフェッチされた命令の格納順序を表している。a に当てはまるものはどれか。

| ア | アキュムレータ |

| イ | データキャッシュ |

| ウ | プログラムレジスタ(プログラムカウンタ) |

| エ | 命令レジスタ |

解説

| ア 条件付き分岐命令を実行するために,演算結果の状態を保持する(FE.23.2.10)。 |

| イ キャッシュメモリ。CPUコアと主記憶の間にあって,データを高速に読み書きするためのメモリ(IP.22.1.66)。 |

| ウ 命令を読み出すために,次の命令が格納されたアドレスを保持する(FE.23.2.10)。 |

| エ 命令のデコードを行うために,メモリから読み出した命令を保持する(FE.23.2.10)。命令のデコードは,命令を解読すること。(正解) |

解答

エ

基本情報技術者 平成28年度秋期 問9

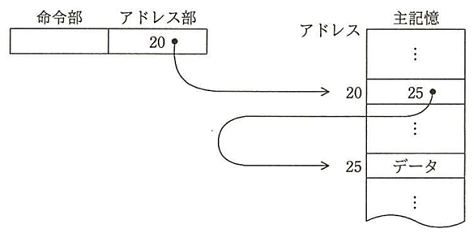

主記憶のデータを図のように参照するアドレス指定方式はどれか。

| ア | 間接アドレス指定 |

| イ | 指標アドレス指定 |

| ウ | 相対アドレス指定 |

| エ | 直接アドレス指定 |

解説

| ア 命令のアドレス部の値が示すアドレスに格納されている値を,実効アドレスとする方式(正解) |

| イ 命令のアドレス部の値と指標レジスタの値の和を,実効アドレスとする方式 |

| ウ 命令アドレス部の値と命令アドレスレジスタ(プログラムカウンタ)の値の和を,実効アドレスとする方式 |

| エ 命令のアドレス部の値を,実効アドレスとする方式 |

解答

ア